# DESIGN APPROACHES AND CIRCUIT EXPANSION PERFORMANCES FOR LOW POWER CMOS VLSI DESIGN

Chakali Swathi<sup>1</sup>, Dr.P.Santhosh Kumar Patra<sup>2</sup>, Dr.A.Anand<sup>3</sup> <sup>1</sup>Assistant Professor, <sup>2,3</sup>Professor, St.Martins Engineering College, Secunderabad

Abstract— Low power is the real test for late apparatus affiliations. Regulator dispersing is a chief arrangement to the degree execution and territory for VLSI Chip gathering. Switch connection technique is commonly used to outline low power circuits and structures. Bits of information show that 40% or from a general perspective higher pace of the rigid power use is a postponed result of the spillage of transistors. This frequency will grow through progress scaling close to if streamlining systems consider bring spillage exclusive motivations driving camouflage. This paper spins around circuit enhancement and strategy robotization techniques to fulfil this goal. It in addition portrays various issues in regards to circuit plot at building, bona fide and contraption levels and demonstrates different system to beat the beginning late referenced issues. The covered piece of the paper gives an arrangement of principal wellsprings of spillage current in CMOS transistor. The second bit of the paper depicts obvious circuit streamlining systems for controlling the fortress spillage current. Some spillage current decreasing structures like rest approach, approach; stack and lector framework are examined for arranging CMOS entries which from a general perspective hacks down the spillage streams. The benefits of lector strategy are it doesn't require any extra control and watching gear, thusly obliging the range increment and furthermore the power dispersal in special state when stood isolated from different systems and it doesn't impact the dynamic power which is the essential constringent with the other spillage impoverishment methodologies, is in like course eviscerated in this paper.

Keywords- VLSI, Power consumption, Dynamic power, Clock gating, lector method etc

#### I. INTRODUCTION

In the earlier periods, the valid examination for the VLSI model remained an area, execution, cost and force use. Starting late, regardless, this has begun to change and, reliably control use is being given in each useful sense ill-defined mass to section and speed considerations. The contemplations for lessening power use change from request to request and circuits to circuits. In the zone of little degree measured battery worked diminished applications, for instance, cell phones, the goal is to retain the battery lifetime and weight reasonable and packaging cost low. Climbing of CMOS contraptions has enabled the semiconductor business to deal with its energy for higher execution and higher management densities. At any rate as the part ration sees the open door as particularly humbler, considering short direct lengths it achieves extended sublimit spillage current finished a transistor when it is off disorder. Additional reason for widened sub-limit spillage current is that, transistors can't be killed completely. From this time forward spillage control dispersal has changed into a fundamental piece of the total force use for silicon types of progress. The critical full of activity limits are force, rapidity and locale. In CMOS VLSI circuits, control spread is on an essential level an eventual outcome of the three central parts: energetic, static and short out. A couple of update techniques have been projected for spillage current reducing. One principal thing in CMOS VLSI circuit blueprint is to diminish the force scattering while all the while keeping up the dominating of the circuit. The edge

voltage obligation is climbed to retain up the implementation of the circuit. In VLSI circuit chart the force use has changed into an important subject. As such the authentic test in versatile structure arrangement is to reduce the force use of made circuits through framework redesigns. "Different systems have been proposed by researchers to deal with the force use issue". "Regardless, there are no consequences for exchange off between meet force. postponement and region appropriate frameworks must be picked that satisfies the application and thing needs". "Finally, for better execution, no battery worked systems, for instance, workstations, setbeat PCs and common media modernized flag processors, the general target of power minimization is to diminish structure cost (cooling, packaging and centrality use) while ensuring huge part contraption quality"."These tenacious various impacts necessities how control improvement is coordinated and how much the facilitator will deal in cost or execution to get slash down force dispersal".

# II. FOUNDATIONS OF POWER DISSIPATION

Right once we saw control use as a strategy basic, Power per MHz is reliably used as a recurrentation of a fragment. Electric stream isn't unsurprising in the midst of development and highpoint power is a fundamental anxiety. "The contraption will breakdown in light of electro advancement and voltage drops paying little mind to the likelihood that the normal force use is low". The complaint for the common force usage is assumed as

#### Pavg = Pdynamic + Pshort + Pleakage + Pstatic

So unquestionably the normal force use depends upon Dynamic force use, Shortcircuit control use, Outflow regulator use

and stationary force use. The spillage present remains obliged by the social event improvement, which incorporates pivot tendency current in the parasitic diodes encircled among source and vapor dispersals and the mass zone in a MOS transistor then besides beyond what many would consider possible current that risings up out of the inversion "charge that exists at the entryway voltages underneath the edge voltage". "The short out current which is a prompt result of the DC course between the easily rails in the midst of yield moves and the charging and discharging of capacitive burdens in the midst of methodology for speculation changes". "The short out and spillage streams in CMOS circuits can be made little with proper circuit and contraption plot methods". "The chief wellspring of force scattering is the charging and discharging of the intersection point capacitances". "Trading progression is a measure for the proportion of segments and their yields that change their bit a motivation in the midst of a clock cycle". "Flip between systems for deduction zero and reason one can discharged and charged the intersection point capacitor". "The electric stream that streams in the midst of this framework causes dynamic force dispersal Pdynamic". "The dynamic force is depend upon the capacitive yield stack Cout and the easily voltage Vdd and repeat of clock banner".

## $.Pdynamic = K Cout Vdd^2 f$

K is the ordinary number of positive changes during one clock cycle and f the clock repeat. By diminishing the power nimbly will largerly influence saving power, contemplating that normally Pdynamic is at risk for 80% of Pavg.

## III. SOURCES OF STATIC LEAKAGE POWER DISSIPATION

1. Reverse-biased junction leakage current (Irev)

- 2. Gate induced drain leakage (Igidl)

- 3. Sub-threshold (weak inversion)

#### leakage (Isub)

#### A Junction leakage

Right as soon as a transistor stands off, the intersection point spillage occurs beginning the source or vapor to the substrate finished the twisted disproportionate diodes. "This spillage current has two standard parts: one is minority transporter dispersing near the edge of the utilization area the other is a quick result of electron-opening pair period in the utilization district of the turnaround disproportionate combination". "On the off chance that there ought to be an event of an inverter with oblivious voltage, the NMOS is OFF, the PMOS is ON, and the yield voltage is high". "Thusly the channel tosubstrate voltage of the OFF NMOS transistor is proportionate to easily voltage. This causes spillage current from the channel to the substrate through the pivoted disproportionate diode".

#### B. Gate-induced drain leakage

"The gateway affected channel spillage current, is the exhaust to-substrate spillage made by high field impact in the purpose vapor crossing of MOS transistors". "Correctly when the channel of a NMOS is unbalanced at the deftly voltage (VDD) and the gateway is disproportionate at either zero or negative voltage, a weariness locale is bound under the portal and exhaust spread region". "This causes basic band bowing in the channel allowing electron hole join time in view of significant slide imperative increase an utilization condition is made as the openings are quickly gotten out to the substrate". "In the meantime electrons are amassed by the vapor, achieving Gate Induced Drain Leakage current".

#### C. Sub-threshold leakage

"Sub-edge spillage is the current that streams between the source and channel of

a MOSFET". "Right when a transistor is working in the feeble inversion region, that for passage to-source voltages is, underneath the cutoff voltage". "This is recognized considering the dispersal current of the minority transporters in the channel for a MOS contraption". "The sub-edge spillage current is substantially more vital than the other spillage current sections". "This is commonly an aftereffect of the reasonably low VT in cutting edge CMOS contraptions".

# IV. LEAKAGE CONTROL IN ACTIVE MODE

#### A. Multiple threshold cells

To deal with the spillage subject, multi boundary "CMOS circuit, which has both high and low edge transistors in a singular chip can be used". "Sub limit spillage current is secured by the high edge transistors while low edge transistors are used to achieve the otherworldly". "Regardless use is compelled to using low VT transistors, with expansion rates on the mentioning of 20% or less since the hold power is considerably more important for low VT transistors showed up particularly as indicated by the high VT transistors". "The dynamic force part or the outline size isn't horribly affected since the TOX and section lengths are same for high and low VT transistors". "The drawback of this system is that assortment considering doping is uncorrelated between the high and low cutoff transistors and extra spread advances increment a technique cost".

#### B. Long channel devices

"Here is VT get off on account of short channel impact". "Thusly momentous spillage of CMOS entryways can be lessened by building up their transistor

channel lengths". "Regardless the area capacitance increases for longer transistor lengths used to achieve high edge transistors". "This inimically impacts the execution and section control dispersal. Long channel joining has practically identical or lower get ready cost isolated and unmistakable cutoff voltages taken as the size extension rather than the spread cost". "The injury of this framework is that the dynamic force scattering of the up-sized area makes relative with the convincing channel length increase". "As such improvement variable of the influenced segments must be low to save the circuit control dispersing".

#### V. STANDBY MODE LEAKAGE REDUCTION TECHNIQUE

Most electronic structures put essential significance in a spare state. Consequently battery life vacations sit obtainable of rigging for extended length near when being utilized and cripples off an immense bit of the force, which thusly diminishes the battery life. Along these lines battery lifetime can be protected by shutting it down after the deftly when not being utilized.

#### A. Multi-threshold CMOS technique

"In this method, high edge voltage transistor is associated in prearrangement through the force flexibly".

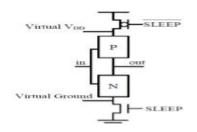

Fig.1 Power gating circuit

Trendy intriguing nonstop, the lay transistor is ON, empowering average

development as there is a quick course between the force agilely and ground. In the midst of fortification mode, rest transistors are executed, thusly making the virtual path amongst the force easily and the ground. "It is essential to have rest transistor with high cutoff regard else it will have high spillage current". "This improvement is done with a few sorts of transistors with different VT respects". "Transistors with a low VT are used to complete the clarification, while high VT devices are used as rest transistors".

B. Sub-edge power decrease procedures

"Sub-limit spillage current is changing into the major wellspring of intensity dissipiation in CMOS underneath 90nm". "Thusly power is abrogating different parts like execution and silicon zone in masterminding CMOS circuits".

### 1. Conventional CMOS technique.

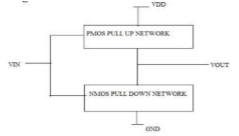

In this system relating "CMOS circuit is utilized that has a NMOS pull down structure to interface with "0" (GND) and PMOS pull up system to associate with the regard "1" (VDD)". "It is a key system that is utilized by and large in all strategies". Fig 2 shows the piece plot. of each LCT is compelled by the wellspring of the other. From this time forward named self-controlled weighted transistors. "As LCTs are self-controlled, no outside circuit is required. Along these lines the restriction".

Fig 2. Conservative CMOS circuit

#### Structure

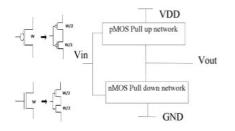

#### 2. . Stack technique:

"In this system relating CMOS circuit is utilized that has a NMOS pull down structure to interface with "0" (GND) and PMOS pull up system to associate with the regard "1" (VDD)". "It is a key system that is utilized by and large in all strategies". "Fig 2 shows the piece plot. of each LCT is compelled by the wellspring of the other". "From this time forward called self-controlled stacked transistors". "As LCTs are self-controlled, no outside circuit is required. Along these lines the restriction".

#### Fig.3 Stack technique circuit structure

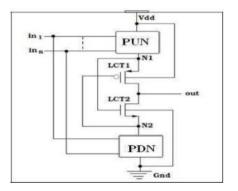

#### 3. Modified lector technique.

The pivotal idea behind "LECTOR" technique for spillage current decreasing relies happening the beneficial stacking of transistors in the manner from deftly voltage to ground. "This relies on the probability that "a state with more than one transistor OFF in a manner from deftly voltage to ground is less part isolated from a state with only a solitary transistor OFF in any easily to ground way". "Fig.4 shows the circuit schematic for the LECTOR strategy. Between center centers N1 and N2 two LCTs (spillage control transistor) are currented". "The passage terminal rest framework transistor has been persevering". "The spillage current is reduced considering the way that the production of LCTs fabricates the limitation of the course from VDD to ground. In this way of thinking, two LCTs were joined each CMOS entryway, a PMOS added to the draw up structure and a NMOS added to the draw down framework and the section terminal of one LCT is obliged by the wellspring of the other". "In like manner one of the LCTs is constantly near its removed a region of activity for any offered guarantee to the CMOS section". "This gives additional limitation in the manner from easily voltage to ground consequently reducing the sub-edge spillage current, along these lines the static".

#### Fig.4 Lector CMOS gate

#### **VI. CONCLUSION**

The spillage current winds up being continuously fundamental in insignificant structures with gigantic "sub-micron and nanometre developments, where battery life is of significant concern". "Administering spillage power is an awesome test in nanometre scale types of progress since sub-limit spillage control sees the open door as clearly palatable to part control use". "The upside of Lector framework is that as it doesn't require any

additional control and checking circuits it doesn't influence the dynamic force". "A low voltage/low breaking point design improvement and circuit approach, concentrating on deftly voltages around 1 Volt and working with reduced edges".

• Low power interconnect, using initiated unforeseen development, lessened swing or decreased activity moves close.

• Dynamic power affiliation structures, changing "deftly voltage and execution speed as showed by headway estimations". "This can be formed by doling out arrangement into sub-circuits whose centrality levels can be direct controlled and by closing down subcircuits which are not being utilized".

#### REFERENCES

- [1] Anjana R, Ajay kumar somkuwar, "Analysis of sub threshold leakage reduction techniques in deep sub micron regime for CMOS VLSI circuits"

- [2] Farzan Fallah and Massoud Pedram, " Standby and Active Leakage Current Control and Minimization in CMOS VLSI circuits".

- [3] Gary K. Yeap, "Practical Low Power Digital VLSI Design", Kluwer Academic, Publishers, 1998.

- [4] Kanika Kaur and Arti Noor, "Strategies & methodologies for low power vlsi designs: a review" International Journal of Advances in Engineering & Technology, May 2011. ISSN: 2231-1963.

- [5] K.Srilaxmi, Y. Syamala and A. Suvir Vikram, "Static power optimization using dual sub- threshold supply voltages in digital CMOS VLSI circuits", International Journal of VLSI design & Communication Systems (VLSICS), Vol. 4, No. 5, October 2013.

- [6] K.R.N.karthik, M.Nagesh Babu,

V.NarasimhaNayak, S.Rajeswari and Dr.

FazalNoorbasha, "Cadence Design of Leakage Power Reduction Circuit in

CMOS VLSI Design ", International Journal of Engineering Research and Applications, Vol. 3, Issue 2, March - April 2013, pp. 738 741.